NAND論理ゲートから他の論理ゲートを作ってみる その2

前回NANDゲートから他のゲートを作りました。

今回は、XOR,マルチプレクサ、一つの入力を二つの出力どちらかに出力させるでマルチプレクサゲートを作っていきます。

なお、今回作成した論理ゲートは前回のブログで作成済みの論理ゲートから作成しております。つまり、こちらの論理ゲートもNANDゲートから作ることができる論理ゲートとなります。今回使用する論理ゲートの仕組みを知りたい方は前回のブログを参照ください。

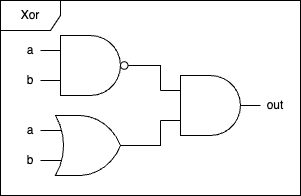

XOR

XORはa,bの内、片方が1の場合は出力が1になる論理ゲートです。

| a | b | out |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

XORの設計・実装

今まで作成した論理ゲートでXORを実現するには以下のような構成で実現できます。

真理値表で一致するか確認します。

| a | b | X=NAND(a b) | Y=OR(a b) | out=AND(X Y) |

|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 0 | 1 | 0 |

一致していますので、上図の構成をもとに実装とテストをしてみます。

def Xor(a:bool,b:bool) -> bool: in1 = Nand(a,b) in2 = Or(a,b) out = And(in1,in2) return out

test_list.extend(gen_t_list(gate.Xor,gen_t_in(2),[0,1,1,0]))

tests/test_gate.py::test_gate[Xor(0, 0) = 0] PASSED tests/test_gate.py::test_gate[Xor(0, 1) = 1] PASSED tests/test_gate.py::test_gate[Xor(1, 0) = 1] PASSED tests/test_gate.py::test_gate[Xor(1, 1) = 0] PASSED

テスト確認も出来たので無事にXORゲートを作成できました。

マルチプレクサ

二つの入力と一つの選択ビットを用いてどちらかの入力を選ぶゲートのことをマルチプレクサと言います。

マルチプレクサは次のような形をとっています。

| a | b | sel | out |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 |

真理値表をしっかり見ると、selが0の時はaの値、selが1の時はbの値が出力されていることがわかるかと思います。

マルチプレクサの設計・実装

今まで作成した論理ゲートでマルチプレクサを実現するには以下のような構成にします。

本当にこれで真理値表が同じになるか確認してみましょう。

| a | b | sel | X=NOT(sel) | Y=AND(X a) | Z=AND(sel b) | out=OR(Y Z) |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 | 1 | 1 |

最後のoutとマルチプレクサの真理値は一致しているので、この構成で作れそうですね。

それでは実装とテストを作ってみましょう。

def Mux(a:bool,b:bool,sel:bool) -> bool: in1 = Not(sel) in2 = And(a,in1) in3 = And(b,sel) out = Or(in2,in3) return out

test_list.extend(gen_t_list(gate.Mux, gen_t_in(3),[0,0,0,1,1,0,1,1]))

tests/test_gate.py::test_gate[Mux(0, 0, 0) = 0] PASSED tests/test_gate.py::test_gate[Mux(0, 0, 1) = 0] PASSED tests/test_gate.py::test_gate[Mux(0, 1, 0) = 0] PASSED tests/test_gate.py::test_gate[Mux(0, 1, 1) = 1] PASSED tests/test_gate.py::test_gate[Mux(1, 0, 0) = 1] PASSED tests/test_gate.py::test_gate[Mux(1, 0, 1) = 0] PASSED tests/test_gate.py::test_gate[Mux(1, 1, 0) = 1] PASSED tests/test_gate.py::test_gate[Mux(1, 1, 1) = 1] PASSED

マルチプレクサも大丈夫そうですね。

デマルチプレクサ

デマルチプレクサは一つの入力を二つの出力のどちらかに出力するというゲートになります。選択にはマルチプレクサと同じく選択ビットを用います。

例えば、selが0ならaの方にINの値が入りますし、1ならbの方にINが入ります。

selに選ばれなかったルートは0になります。

この挙動を心理地表で表すと以下のようになります。

| in | sel | a | b |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

デマルチプレクサの設計と実装

今まで作成した論理ゲートでデマルチプレクサを実現する方法として、以下のような構成を考えました。

他のゲートと同じく真理値表で確かめてみます。

| in | sel | NOT(sel) | a = AND(in NOT(sel)) | b = AND(in sel) |

|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

a,bは一致しているので、この構成で大丈夫そうです。

上の図をもとに実装とテストは下記のように作成しました。

def DMux(_in:bool,sel:bool) -> tuple[bool,bool]: nsel = Not(sel) out1 = And(_in,nsel) out2 = And(_in,sel) return (out1,out2)

test_list.extend(gen_t_list(gate.DMux,gen_t_in(2),[(0,0),(0,0),(1,0),(0,1)]))

tests/test_gate.py::test_gate[DMux(0, 0) = (0, 0)] PASSED tests/test_gate.py::test_gate[DMux(0, 1) = (0, 0)] PASSED tests/test_gate.py::test_gate[DMux(1, 0) = (1, 0)] PASSED tests/test_gate.py::test_gate[DMux(1, 1) = (0, 1)] PASSED

テストもパスしたので、デマルチプレクサも無事に作成できました。

今回のブログで、基本的に使われる論理ゲートは全て作れましたかね。

次回はこれらのゲートを組み合わせて加算器を作りたいと思います、

次回もお楽しみに、またお会いしましょう。